# Supercapacitor Charger and Ideal Diode for Power Supply Ride-Through Systems

George H. Barbehenn

Supercapacitors, capacitors with up to 100F of charge storage, are emerging as an alternative to batteries in applications where the importance of power delivery trumps that of total energy storage. Supercapacitors have a number of advantages over batteries that make them a superior solution when short term, high power is needed, such as in power ride-through applications. These advantages include lower effective series resistance (ESR) and enhanced durability in the face of repeated charging.

Like batteries, supercapacitors have some specialized application needs that make using a dedicated IC desirable. Supercapacitor technology can now offer capacitors as large as 100F, but the maximum working voltage on these capacitors is 2.7V or less. Because most systems require operating voltages higher than this, many supercapacitors are

The maximum working voltage on a single supercapacitor is 2.7V or less. Because most systems require operating voltages higher than this, many supercapacitors are supplied as a pair of capacitors within a single, center-tapped package. The LTC4425 is designed to to charge stacked supercapacitors and provide a regulated output voltage for the system load.

supplied as a pair of capacitors within a single, center-tapped package. The LTC4425 is designed to charge two stacked supercapacitors and provide a regulated output voltage for the system load.

**THE LTC4425 ARCHITECTURE** The LTC4425 has two modes of operation: Normal and LDO.

#### **Normal Mode**

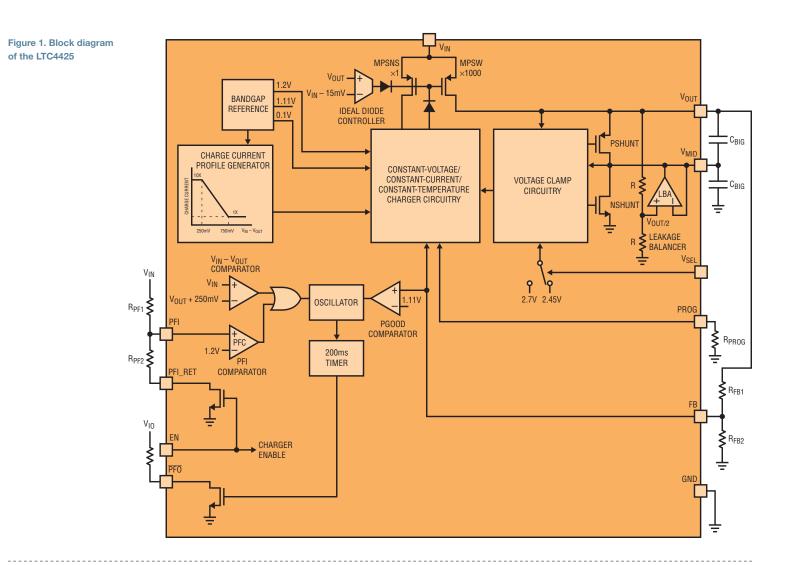

In Normal mode, the LTC4425 can be thought of as an ideal diode with current limit and supercapacitor-specific functions (see Figure 1). If we ignore everthing but the ideal diode controller, MPSNS and MPSW, the LTC4425 behaves like an ideal diode. MPSW is turned on whenever  $V_{OUT}$  is lower than  $V_{IN}$  by more than 15mV.

A fraction (1/1000) of the current in the  $v_{OUT}$  pin is impressed on the resistor attached to the PROG pin and the resultant voltage is compared to a reference voltage. When the voltage on the PROG pin reaches the reference voltage, no additional current is allowed to flow out of the  $v_{OUT}$  pin.

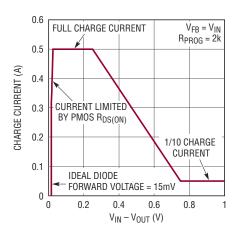

In Normal mode, the regulation function is not controlled by the output voltage alone, but by  $v_{IN} - v_{OUT}$  (see Figure 2). Normal mode is selected by connecting the FB pin to  $v_{IN}$ . In Normal mode, as long as  $v_{IN} - v_{OUT}$  is greater than 0.75V, the charge current is 1/10 the programmed value. As the  $v_{IN} - v_{OUT}$  voltage decreases from 0.75V to 0.25V, the charge current increases linearly to the programmed value at  $v_{IN} - v_{OUT} = 0.25V$ . For  $v_{IN} - v_{OUT}$  voltages less than 0.25V, but greater than 15mV, the  $v_{OUT}$  current is 1000/R<sub>PROG</sub>, and can be as high as 2A. However, the MPSW device

Figure 2. Supercapacitor charge current profile in Normal mode is designed to prevent inrush currents

has an  $R_{DS(ON)}$  of approximately 50m $\Omega$ , so when  $V_{IN} - V_{OUT}$  is small enough, this resistance may limit the current. For  $V_{IN} - V_{OUT}$  voltages less than 15mV, the ideal diode shuts off, reducing the current out of  $V_{OUT}$  to a small leakage current.

## LDO Mode

In LDO mode the regulation function is not controlled by  $v_{IN} - v_{OUT}$ , but by feedback from the output voltage. LDO mode is chosen by connecting an output voltage divider to the FB pin to set the maximum output voltage. In LDO mode, the LTC4425 behaves like a voltage regulator supplying up the programmed current to the load and to charge the supercapacitor. If the supercapacitor is at the desired voltage, the LTC4425 continues to supply the load current up to the programmed maximum current.

If the desired supercapacitor voltage is as close to  $v_{IN}$  as possible, then ground the FB pin. This means that the loop will never reach regulation, but the output voltage

will track the input voltage within 15mV or  $I_{V(OUT)} \times R_{DS(ON)}$ , whichever is larger.

The LTC4425 limits the current available to the  $v_{OUT}$  pin. Usually this current is used to charge the supercapacitor, but could also go to a load. In LDO mode, the current is limited in two ways, the PROG pin, and thermal limiting.

The PROG reference voltage, used in LDO mode, is 1V, and the fraction of the  $V_{OUT}$  current that is impressed on the resistor attached to the PROG pin is 1/1000. So the current limit is 1000/  $R_{PROG}$ , and can be as high as 2A.

If one imagines charging a 100F capacitor, even at 2A, the voltage changes at 20mV/s. And, during this charging process there is significant dissipation, usually several watts. If a portion of the V<sub>OUT</sub> current is going to a system load, then the time to charge the supercapacitor is extended. The LTC4425 has a linear thermal regulation loop that limits the current from V<sub>OUT</sub>, such that the die temperature remains below 105°C. This is a linear circuit meant for usage under normal operating conditions, not a protection circuit that is only there to prevent damage.

#### **LTC4425 FEATURES**

#### Voltage Clamps

There are voltage clamps on each of the stacked output supercapacitors, from  $v_{OUT}$  to  $v_{MID}$ , and from  $v_{MID}$  to ground. The purpose of these voltage clamps is to ensure that the supercapacitors cannot be charged above their rated voltages. The clamp voltage on each of the

$V_{OUT} \cong V_{IN}$

**≥**470k

2k

IMONITOR

PFO

PROG

TO HIGH PEAK

POWER LOAD

The LTC4425 detects any imbalance in the stacked supercapacitors by comparing V<sub>MID</sub> to V<sub>OUT</sub>. When the LTC4425 detects an imbalance, it sinks or sources current from the V<sub>MID</sub> pin to balance the supercapacitor.

2.2µF **₹** 1.5M

PFI

1.2N

PFI RET

FROM µC

SEL

ΕN

2.45V/2.7V

GND

Ŧ

l i-lor

stacked supercapacitors can be selected to be 2.45V or 2.70V, via the SEL pin.

Suppose that the input voltage is 6v, and the FB pin is grounded, so that the LTC4425 is in LDO mode and trying to charge the supercapacitor to the input voltage. The clamps will activate whenever either of the stacked supercapacitors exceed the clamp voltage.

To keep the power dissipation in the clamp circuitry in check, the LTC4425 automatically reduces the charge current to 1/10 of the programmed value whenever either of the stacked supercapacitors approaches the clamp voltage.

### Leakage Balancer

The LTC4425 detects any imbalance in the stacked supercapacitors by comparing  $v_{MID}$  to  $v_{OUT}$ . When the LTC4425 detects an imbalance, it sinks or sources current from the  $v_{MID}$  pin to balance the supercapacitor.

The LTC4425 leakage balancer is primarily intended to account for the effects of self, or system leakage, and so the maximum sink or source current is around 1mA. Nevertheless, the interaction of the voltage clamps and leakage balancer will eventually correct even quite large imbalances. The supercapacitor may become unbalanced during charging because one capacitor in the stack is larger or smaller than the other. For the same charge current, the larger capacitor will be a lower voltage than the smaller capacitor. So, the smaller capacitor may activate its voltage clamp before the larger capacitor finishes charging, unbalancing the stack.

The leakage balancer will then engage and slowly bring the stack back into balance.

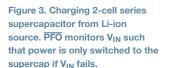

## **PFO** Output

The LTC4425 monitors and reports conditions of  $v_{IN}$  and  $v_{OUT}$  depending on the mode.  $\overline{PFO}$  goes low if the PFI pin is below 1.2V or  $(v_{IN} - v_{OUT}) > 250mV$  (in Normal mode) or  $v_{FB} < 1.11V$  (in LDO mode), so  $\overline{PFO}$  can be used to switch the load to the supercapacitor if there is a loss of  $v_{IN}$  (see Figure 3).

This is especially useful if the load current is much higher than the maximum current the LTC4425 can supply. PFO can be used to switch the load to the super-capacitor *only* in the absence of  $v_{IN}$ .

Note that  $\overline{PFO}$  monitors either an input fault, or it indicates a low output voltage at the FB pin. If the FB pin is grounded—that is, setup in LDO mode to charge the supercapacitor to  $v_{IN}$ —then  $\overline{PFO}$  is permanently asserted low, masking any faults on  $v_{IN}$ .

# SUPERCAPACITOR-BASED RIDE-THROUGH SYSTEM

LTC4425

Many electronics systems require a short-term power backup system that allows them to ride through brief interruptions in power. In a similar vein, some systems need time to save states, or empty volatile memory or perform other housekeeping tasks when power is abruptly removed. For example, a hard drive may need to park the heads, so that they don't land on the media surface. This is an electromechanical system that requires 20ms–100ms of continuous power before it can completely shut down.

Another example involves the effect of large electrical machines on power systems. If a large electric motor is started, such as a commercial building air conditioner or elevator, the mains supply may collapse for several line cycles. Usually the input supply stores only enough energy for between a half a cycle and one cycle. Devices powered by the input supply need a way to operate normally until the mains recovers. Supercapacitors are well suited to short-power-burst, ride-through applications. Their low source impedance allows them to supply significant power for a relatively short time, and they are considerably more robust than batteries.

Ride-through applications can certainly be implemented with battery backup, but in many cases, it requires a very large battery array to satisfy the ride-through power requirements. Although batteries can store a lot of energy, they cannot supply much power per volume due to their significant source impedance. Batteries also have relatively short lives, 2~3 years, and their care and feeding requirements are substantial.

Supercapacitors, on the other hand, are well suited to short-power-burst, ride-through applications. Their low source impedance allows them to supply significant power for a relatively short time, and they are considerably more robust than batteries.

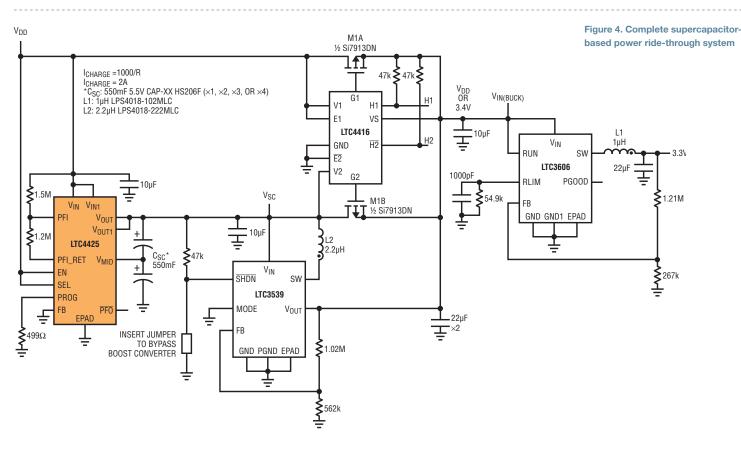

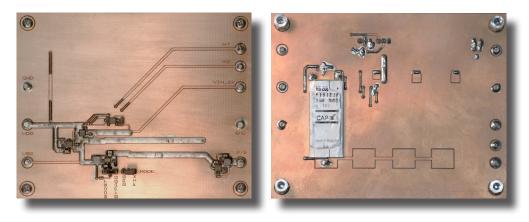

**Ride-Through Application Setup** Figure 4 shows a complete power interruption ride-through system using the LTC4425, LTC4416, LTC3539 and LTC3606. Figure 5 shows the layout. This design can hold up a 3.3V rail at 200mA for almost eight seconds.

The LTC3606 is a micropower buck regulator that produces 3.3V. The LTC4416 provides a dual ideal diode-OR function to ensure maximum efficiency when switching from the regular input to the supercap. The LTC3539 is a micropower boost regulator with output disconnect. This boost regulator operates down to 0.5V, and can support loads of  $1.3A \times$ V<sub>OUT</sub>/V<sub>IN</sub> at its output. The supercapacitor is a CAP-XX HS206F, 0.55F, 5.5V capacitor.

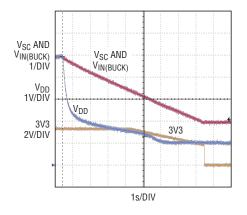

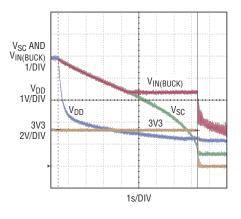

**Ride-Through Application Measured Results and Operation Details** Figure 6 shows the waveforms if the LTC3539 boost circuit is disabled. Run time, from input power off to output regulator voltage dropping to 3v, is 4.68s. Figure 7 shows the waveforms if the LTC3539 boost circuit is operational. Run time, from input power off to output regulator dropping to 3v, is 7.92s. One way to extend the ride-through time for a given supercapacitor is to add a boost regulator to the system, which allows for energy scavenging. The run time of a given supercapacitor can be extended by >30% if energy scavenging is used.

When the LTC3539 boost regulator is disabled, as soon as input power falls, the LTC4416 based ideal diodes switch the input energy supply for the LTC3539 buck regulator to the supercap. In Figure 6, the voltage across the supercap ( $v_{sC}$ ) linearly decreases due to the constant power load of 200mA at 3.3V on the buck regulator ( $v_{OUT}$ ).

When the input voltage to the LTC3539 reaches the dropout voltage of the regulator, the output voltage is seen to track the input voltage. At 4.68s after input power removal, the voltage on the supercap reaches 3.0v plus the dropout voltage, and  $v_{OUT}$  drops below 3v. The buck regulator continues to track the supercap voltage down until it reaches 2v, whereupon the buck regulator shuts off.

In Figure 7, the voltage across the supercap  $(v_{SC})$  linearly decreases due to the constant power load of 200mA at 3.3V on the buck regulator. When  $v_{SC}$  reaches 3.4V, the regulation point of the boost regulator, the boost regulator begins switching. This shuts off the ideal diode and disconnects the buck regulator from the supercapacitor. The energy input to the buck regulator of 3.4V.  $v_{SC}$  remains at 3.4V, but the supercap begins to discharge exponentially, because as the input voltage of the boost regulator drops, it must draw higher and higher current to sustain its output at 3.4V.

Because the input of the buck regulator remains at 3.4v, its output remains in regulation. When the boost regulator reaches its input UVLO it shuts off,

Figure 5. Front and back board layout used to test the circuit in Figure 4

and its output immediately collapses. Since its input voltage has now collapsed, the buck regulator shuts off.

Energy Scavenging in the Ride-Through Application

What voltage should the boost output be set to? Clearly, operation is identical, with or without the boost circuit enabled until the input dropout of the buck regulator is reached. One goal in the design

Figure 6. If the boost regulator is disabled in the circuit of Figure 4, the ride-through applications can support a 0.67W load for about 4.68s.

is to minimize the amount of time that the boost regulator is used in the power chain, because each additional regulation step lowers the overall efficiency. Here, we set the boost regulator output voltage as close to the buck regulator input dropout voltage as possible, or 3.4v.

The boost regulator must have a synchronous output to maximize efficiency once the boost regulator engages. This

continued on page 31

Figure 7. With boost regulator enabled in the circuit of Figure 4, the ride-through applications can support a 0.67W load for about 7.92s.

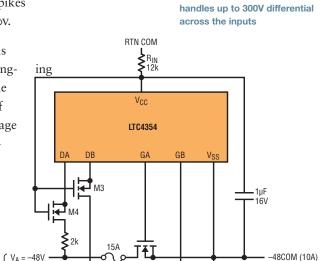

Figure 3. The LTC4354 shown in a 10A,–48V application

Zeners in the 250mW to 500mW range are capable of absorbing the peak current generated by a 150V, 10µs spike. Higher voltage and longer duration spikes may be accommodated by larger devices.

bias is conveniently obtained from the shunt-regulated  $v_{CC}$  pin without the need for any extra components, making this useful configuration a very simple modification of the basic circuit.

Under normal conditions, the -48v inputs are at or near the v<sub>SS</sub> potential, and the small MOSFETS M3 and M4 are driven fully on as their gates are biased to ~11v with respect to v<sub>SS</sub> by the v<sub>CC</sub> pin. If one input rises with respect to v<sub>SS</sub>, the small MOSFET remains on and the associated drain pin tracks the input. If the input continues to rise to the point where it is  $\geq$ 10v with respect to v<sub>SS</sub>, the small MOSFET turns into a source follower, safely limiting the drain pin to about 10v with respect to v<sub>SS</sub>. MOSFETS

supercap charger, continued from page 19 implies a boost regulator with a "blocking" output. This in turn necessitates the second ideal diode to allow the supercapacitor to power the buck regulator until the boost regulator engages. The boost regulator must operate to as low a voltage as possible to ensure that the maximum amount of energy is scavenged from the supercapacitor.

If the supercapacitor is initially charged to 5v, then the energy in the supercapacitor is:

$$\frac{1}{2}CV^2 = \frac{1}{2}0.55F \bullet 5^2 = 6.875J$$

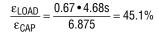

The output power is 3.33V at 0.2A = 0.67W, so the percentage of the energy stored in the supercap that is extracted with a buck-only circuit is: M1 and M2 can be expected to avalanche and clamp any positive-going spikes exceeding 300v, to less than 400v.

While the circuit in Figure 3 was designed for a -48v system, chang-R<sub>IN</sub> to a 100k, 1W unit allows the circuit to operate with inputs of -200V to -300V DC. Higher voltage standoff is possible with appropriate selection of MOSFETS.

T₹]

21

M1, M2: IXTT 1XTT88N30P

M3. M4: DIODES INC. ZVN0540A

15A

The percentage of the energy stored in the supercap, extracted when the boost regulator is enabled, is:

300V MAX

DIFFERENTIAL VOLTAGE

$$\frac{\varepsilon_{\text{LOAD}}}{\varepsilon_{\text{CAP}}} = \frac{0.67 \cdot 7.92\text{s}}{6.875} = 77\%$$

The percentage of energy stored in the supercapacitor that is recovered increases from 45.1% to 77%. This allows use of a smaller, less expensive supercapacitor.

# CONCLUSION

The power ride-through system shown here uses a 0.55F supercap to hold up power long enough for a microcontroller to complete some last gasp housekeeping tasks. One way to extend the ride-through time for a given supercapacitor is to add a boost regulator to the system, which allows for energy scavenging. The run time of a given supercapacitor can be extended by >30% if energy scavenging is used. This is particularly relevant if the supercapacitor operating voltage is reduced to ensure high temperature reliability.

In addition, the shape of the output voltage is considerably improved as the input voltage to the output regulator is now square in shape. This results in a steady 3.3V output voltage with a sharp cutoff, instead of a ramped voltage drop as the supercap drains.